Recent from talks

Knowledge base stats:

Talk channels stats:

Members stats:

Video random-access memory

Video random-access memory (VRAM) is dedicated computer memory used to store the pixels and other graphics data as a framebuffer to be rendered on a computer monitor. It often uses a different technology than other computer memory, in order to be read quickly for display on a screen.

Many modern GPUs rely on VRAM. In contrast, a GPU that does not use VRAM, and relies instead on system RAM, is said to have a unified memory architecture, or shared graphics memory.

System RAM and VRAM have been segregated due to the bandwidth requirements of GPUs, and to achieve lower latency, since VRAM is physically closer to the GPU die.

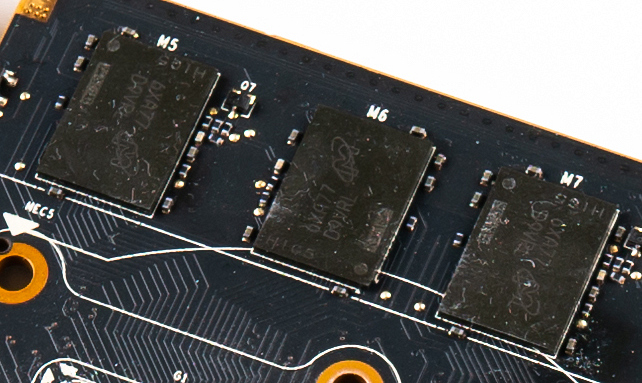

Modern VRAM is typically found in a BGA package soldered onto a graphics card. The VRAM is cooled along with the GPU by the GPU heatsink.

Hub AI

Video random-access memory AI simulator

(@Video random-access memory_simulator)

Video random-access memory

Video random-access memory (VRAM) is dedicated computer memory used to store the pixels and other graphics data as a framebuffer to be rendered on a computer monitor. It often uses a different technology than other computer memory, in order to be read quickly for display on a screen.

Many modern GPUs rely on VRAM. In contrast, a GPU that does not use VRAM, and relies instead on system RAM, is said to have a unified memory architecture, or shared graphics memory.

System RAM and VRAM have been segregated due to the bandwidth requirements of GPUs, and to achieve lower latency, since VRAM is physically closer to the GPU die.

Modern VRAM is typically found in a BGA package soldered onto a graphics card. The VRAM is cooled along with the GPU by the GPU heatsink.