Recent from talks

Nothing was collected or created yet.

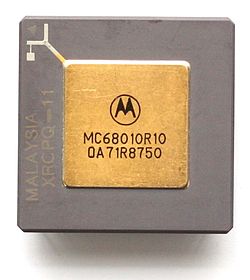

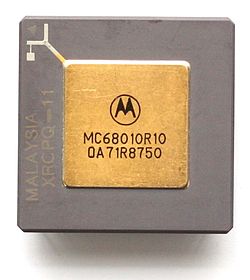

Motorola 68010

View on Wikipedia| General information | |

|---|---|

| Launched | 1982 |

| Designed by | Motorola |

| Performance | |

| Max. CPU clock rate | 8 MHz to 16.67 MHz |

| Data width | 16 bits |

| Address width | MC68010: 24 bits MC68012: 31 bits |

| Architecture and classification | |

| Instruction set | Motorola 68000 series |

| Physical specifications | |

| Transistors |

|

| Packages | |

| History | |

| Predecessor | Motorola 68000 |

| Successor | Motorola 68020 |

The Motorola MC68010 and Motorola MC68012 are 16/32-bit microprocessors from Motorola, released in 1982 as successors to the Motorola 68000.[3] The 68010 and 68012 added virtualization features, optimized loops and fixed several small flaws to the 68000. The MC68010 variants were pin compatible with its predecessor while the MC68012 is an 84-pin PGA version with its directly accessible memory space extended to 2 GiB.[2][4]

Differences between 68010/68012 and 68000

[edit]The 68010 and 68012 are completely user-mode compatible with the 68000, except that the MOVE from SR instruction traps in user mode, so that, to support user-mode code using that instruction, a supervisor-mode trap handler must simulate the instruction and continue the user-mode code after that instruction. This was done so that the 68010 and 68012 would meet the Popek and Goldberg virtualization requirements, specifically that a new OS could run as guest and not be aware.[2]: §1.3.2 A new unprivileged MOVE from CCR instruction was added to compensate for the penalty of trapping user-mode MOVE from SR.

The 68010 and 68012 can recover from bus faults, and continue the faulting instruction, allowing them to implement virtual memory. This means that the exception stack frame is different.

A 32-bit Vector Base Register (VBR) holds the base address for the exception vector table. The 68000 vector table was always based at address zero.

A "loop mode" accelerates loops consisting of only a "loopable" instruction and a DBcc (Decrement/Branch on condition); an example would be MOVE and DBRA. The two-instruction mini-loop opcodes are prefetched and held in the 6-byte instruction cache while subsequent memory read/write cycles are only needed for the data operands for the duration of the loop.[2]: §7.1.3 It provided for performance improvements averaging 50%, as a result of the elimination of instruction opcodes fetching during the loop.

The MC68012 variant, in addition to its memory space being extended to 2 GiB, also added a read-modify-write cycle (RMC) pin, indicating that an indivisible read-modify-write cycle in progress, in order to help the design of multiprocessor systems with virtual memory.

The expansion of the memory space in the 68012 caused an issue for any programs that used the high byte of an address to store data, a programming trick that was successful with those processors that only have a 24-bit address bus (68000 and 68010). A similar problem affected the 68020.

Usage

[edit]

The 68010 could be used with the 68451 MMU. However, aspects of its design, such as its 1 clock memory access penalty, made this configuration unpopular. Some vendors used their own MMU designs, such as Sun Microsystems in their Sun-2 workstation and Convergent Technologies in the AT&T UNIX PC/3B1.

The 68010 was never as popular as the 68000 in the years when it was available. However, because of the 68010's small speed boost over the 68000 and its support for virtual memory, it can be found in a number of smaller Unix systems, both with the 68451 MMU (for example in the Torch Triple X), and with a custom MMU (such as the Sun-2 workstation, AT&T UNIX PC/3B1, Convergent Technologies MiniFrame, Plexus P/15 and P/20,[5] NCR Tower XP, Apollo Computer's DN300 and DN320,[6] and HP 9000 Model 310), as well as various research machines. Most other vendors (such as Apple Computer) stayed with the 68000 until the 68020 was introduced.

The 68010 was used on some arcade video games, most notably Marble Madness for the Atari System 1. Some owners of Amiga and Atari ST computers and even Sega Genesis game consoles replaced their system's 68000 CPU with a 68010 to gain a small speed boost.[7][8] In practice, the overall speed gain over a 68000 at the same frequency is less than 10%.

References

[edit]- ^ "i486, 68040 Use Pipelining To Speed Up Performance". InfoWorld: 39. May 8, 1989.

- ^ a b c d e f g MC68010/MC68012 16-/32-Bit Virtual Memory Microprocessors (PDF). Motorola Semiconductor. May 1985. Archived (PDF) from the original on 2020-03-28.

- ^ "Motorola 68010 (MC68010) family". CPU World.

- ^ Avtar, Singh; Triebel, Walter A. (1991). 16-Bit and 32-Bit Microprocessors: Architecture, Software, and Interfacing Techniques. Englewood Cliffs, New Jersey: Prentice-Hall. ISBN 978-0138121570.

- ^ "Plexus P/15-P/20 Brochure" (PDF). UserManual.wiki. Plexus Computers, Inc. 1985. Retrieved 2024-05-28.

- ^ "Apollo Computer Technical Publications Overview" (PDF). Apollo Computer. June 1987. Retrieved 2022-10-13.

- ^ Floryan, Thad. "AMIGA (tm) TECHNICAL NOTE Upgrading an AMIGA A1000 with a Motorola MC68010L8".

- ^ "Genesis 68010 mod". mode5.net.

External links

[edit]Motorola 68010

View on GrokipediaIntroduction and history

Overview

The Motorola 68010 is a 16/32-bit complex instruction set computing (CISC) microprocessor developed by Motorola and released in 1982 as a minor upgrade to the original 68000.[4] It belongs to the influential M68000 family of processors, which were widely used in early personal computers, workstations, and embedded systems due to their balance of performance and compatibility.[7] The 68010 was designed primarily to address key limitations of the 68000, including inadequate support for virtual memory management and inefficiencies in loop execution, while ensuring full backward compatibility with existing 68000 software and hardware.[7] This allowed it to serve as a drop-in replacement in many systems, facilitating upgrades without major redesigns. Initial variants operated at clock speeds ranging from 8 MHz to 16.67 MHz.[8] The processor features approximately 69,000 transistors. It maintains pin compatibility with the 68000 in corresponding packages, such as the 64-pin DIP, simplifying integration into existing motherboards.[4] A related variant, the 68012, extends the 68010's addressing capabilities to 32 bits externally while retaining core compatibility.[4]Development and release

The Motorola 68010 emerged as a direct successor to the Motorola 68000, a 16/32-bit microprocessor introduced in 1979 that achieved widespread adoption in early personal computers and workstations due to its advanced architecture and performance. Despite this success, the 68000 had notable architectural shortcomings, including non-restartable bus errors that prevented reliable handling of page faults and made integration with memory management units (MMUs) challenging for virtual memory systems. These limitations impeded support for multitasking operating systems like Unix variants, prompting Motorola to prioritize enhancements in the next iteration of its 68k family.[7][9] Motorola's design team focused on rectifying these flaws to evolve the 68000 family toward more robust, high-end computing capabilities, including better error recovery and loop optimization to improve efficiency in small, repetitive code sequences common in system software. The 68010 maintained essential compatibility with the 68000 while introducing mechanisms for restartable instructions, enabling seamless virtualization without requiring extensive software rewrites. This evolution positioned the processor as part of Motorola's broader strategy to compete in professional and scientific computing markets demanding advanced OS features.[7][5] Introduced in 1982, the 68010 became commercially available in mid-1983 and was marketed primarily as a drop-in upgrade for existing 68000-based designs, leveraging pin compatibility to facilitate adoption in systems requiring MMU support. Official data sheets detailing its specifications were published by Motorola in May 1985, providing comprehensive documentation for engineers integrating the chip into new hardware.[7][5][10]Architecture and compatibility

Core design

The Motorola 68010 features a 32-bit internal architecture, including eight 32-bit data registers (D0–D7) and eight 32-bit address registers (A0–A7, with A7 serving as the stack pointer). Additionally, it includes three new supervisor-mode registers: the 32-bit Vector Base Register (VBR) for relocating the exception vector table, and the 3-bit Status Function Code (SFC) and Data Function Code (DFC) registers for specifying function codes during CPU-generated bus cycles.[3] It employs a 16-bit external data bus and a 24-bit address bus, enabling access to a 16 MB address space.[3] This design maintains the core register model of the 68000 family while optimizing for enhanced performance through internal enhancements.[2] The processor operates in two modes: supervisor mode for privileged operations and user mode for application execution, ensuring protected access to system resources.[3] User-mode instructions are fully compatible with those of the MC68000, allowing seamless execution of existing application code without modification.[3] The bus interface is asynchronous, mirroring the MC68000's structure to support byte, word, and long-word data transfers, which facilitates integration into existing 68000-based systems.[3] This compatibility extends to pin-for-pin interchangeability, simplifying upgrades.[3] Housed in a typical 64-pin dual in-line package (DIP), the 68010 operates at 5 V and dissipates approximately 1–2 W of power at 10 MHz frequencies, balancing performance with thermal efficiency in embedded applications.[3][11] While user-mode object code is fully compatible with the MC68000, supervisor-mode operations introduce changes—such as new instructions and exception handling mechanisms—that require operating system adjustments for complete functionality.[3]Instruction set enhancements

The Motorola 68010 retains the full instruction set of the MC68000, comprising approximately 56 base instruction types that support a variety of data movement, arithmetic, logical, and control operations essential for structured programming.[12] This compatibility ensures that existing MC68000 software runs without modification on the 68010, with the core set focused on byte, word, and long-word operations across multiple addressing modes.[3] However, to address security concerns in multitasking environments and facilitate integration with memory management units (MMUs), the 68010 introduces targeted modifications that enhance privilege separation without broadly expanding the instruction repertoire.[13] A key enhancement is the addition of the unprivileged MOVE from CCR instruction, which allows user-mode programs to read the contents of the Condition Code Register (CCR)—containing flags for extend (X), negative (N), zero (Z), overflow (V), and carry (C)—and store them zero-extended to a word in a destination effective address.[12] This instruction, unavailable on the MC68000, compensates for restrictions on broader register access by providing a safe mechanism for user-level code to inspect arithmetic results without invoking a privilege violation exception.[12] In syntax, it operates as MOVE CCR,<ea> denotes any valid effective address, and it does not affect the CCR itself during execution.[12]

To bolster operating system security, the 68010 modifies the MOVE from SR instruction, making it privileged such that attempts to execute it in user mode now generate a privilege violation exception, trapping to supervisor mode.[12] On the MC68000, this instruction could be performed in user mode, potentially exposing supervisor bits like the supervisor/user (S) flag and interrupt mask levels, which risked compromising system integrity in virtualized setups.[12] The change enforces stricter isolation, requiring supervisor privilege for accessing the full Status Register (SR), which combines the CCR with additional control bits, thereby optimizing the 68010 for secure OS implementations alongside MMU usage.[13]

Exception handling receives subtle optimizations in the 68010 to support transparent recovery from bus errors, particularly during memory accesses in virtual memory systems.[3] This restartability allows affected instructions—such as those involving data fetches or stores—to resume execution from the point of interruption after the error is resolved by the MMU or handler, using an expanded 26-word exception stack frame that includes fault addresses and status details.[13] Unlike the MC68000's simpler 7-word frame, this mechanism enables precise continuation without full instruction re-execution in many cases, reducing overhead for page faults while maintaining backward compatibility for non-MMU scenarios.[13]

The addressing modes remain unchanged from the MC68000, preserving support for register direct, immediate, absolute, program counter relative, register indirect, and indexed variants to ensure seamless code portability.[12] These modes, exemplified by operations like MOVE D0, (A1)+ for post-increment indirect or ADD #5, D2 for immediate addition, continue to facilitate efficient memory and register manipulations without requiring recompilation.[12] Overall, these enhancements prioritize MMU-friendly operations and security refinements over wholesale additions, positioning the 68010 as a bridge to more advanced 68000-family processors.[3]