NOR logic

View on WikipediaThis article needs additional citations for verification. (October 2025) |

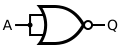

A NOR gate or a NOT OR gate is a logic gate which gives a positive output only when both inputs are negative.

Like NAND gates, NOR gates are so-called "universal gates" that can be combined to form any other kind of logic gate. For example, the first embedded system, the Apollo Guidance Computer, was built exclusively from NOR gates, about 5,600 in total for the later versions. Today, integrated circuits are not constructed exclusively from a single type of gate. Instead, EDA tools are used to convert the description of a logical circuit to a netlist of complex gates (standard cells) or transistors (full custom approach).

NOR

[edit]A NOR gate is logically an inverted OR gate. It has the following truth table:[1]

| ||||||||||||||||

|

Q = A NOR B

| ||||||||||||||||

Making other gates by using NOR gates

[edit]A NOR gate is a universal gate, meaning that any other gate can be represented as a combination of NOR gates.

NOT

[edit]This is made by joining the inputs of a NOR gate. As a NOR gate is equivalent to an OR gate leading to NOT gate, joining the inputs makes the output of the "OR" part of the NOR gate the same as the input, eliminating it from consideration and leaving only the NOT part.

| Desired NOT Gate | NOR Construction |

|---|---|

|

|

| Q = NOT( A ) | = A NOR A |

| Input A | Output Q |

|---|---|

| 0 | 1 |

| 1 | 0 |

OR

[edit]An OR gate is made by inverting the output of a NOR gate. Note that we already know that a NOT gate is equivalent to a NOR gate with its inputs joined.

| Desired OR Gate | NOR Construction |

|---|---|

|

|

| Q = A OR B | = ( A NOR B ) NOR ( A NOR B ) |

| Input A | Input B | Output Q |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

AND

[edit]An AND gate gives a 1 output when both inputs are 1. Therefore, an AND gate is made by inverting the inputs of a NOR gate. Again, note that a NOR gate is equivalent to a NOT with its inputs joined.

| Desired AND Gate | NOR Construction |

|---|---|

|

|

| Q = A AND B | = ( A NOR A ) NOR ( B NOR B ) |

| Input A | Input B | Output Q |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

NAND

[edit]A NAND gate is made by inverting the output of an AND gate. The word NAND means that it is not AND. As the name suggests, it will give 0 when both the inputs are 1.

| Desired NAND Gate | NOR Construction |

|---|---|

|

|

| Q = A NAND B | = [ ( A NOR A ) NOR ( B NOR B ) ] NOR [ ( A NOR A ) NOR ( B NOR B ) ] |

| Input A | Input B | Output Q |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

XNOR

[edit]An XNOR gate is made by connecting four NOR gates as shown below. This construction entails a propagation delay three times that of a single NOR gate.

| Desired XNOR Gate | NOR Construction |

|---|---|

|

|

| Q = A XNOR B | = [ A NOR ( A NOR B ) ] NOR [ B NOR ( A NOR B ) ] |

| Input A | Input B | Output Q |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Alternatively, an XNOR gate is made by considering the conjunctive normal form , noting from de Morgan's Law that a NOR gate is an inverted-input AND gate. This construction uses five gates instead of four.

| Desired Gate | NOR Construction |

|---|---|

|

|

| Q = A XNOR B | = [ B NOR ( A NOR A ) ] NOR [ A NOR ( B NOR B ) ] |

XOR

[edit]An XOR gate is made by considering the conjunctive normal form , noting from de Morgan's Law that a NOR gate is an inverted-input AND gate. This construction entails a propagation delay three times that of a single NOR gate and uses five gates.

| Desired XOR Gate | NOR Construction | |||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

| |||||||||||||||

| Q = A XOR B | = [ ( A NOR A ) NOR ( B NOR B ) ] NOR ( A NOR B ) | |||||||||||||||

| ||||||||||||||||

Alternatively, the 4-gate version of the XNOR gate can be used with an inverter. This construction has a propagation delay four times (instead of three times) that of a single NOR gate.

| Desired Gate | NOR Construction |

|---|---|

|

|

| Q = A XOR B | = { [ A NOR ( A NOR B ) ] NOR [ B NOR ( A NOR B ) ] } NOR { [ A NOR ( A NOR B ) ] NOR [ B NOR ( A NOR B ) ] } |

See also

[edit]- NAND logic — Like NOR gates, NAND gates are also universal gates.

- Functional completeness

References

[edit]- ^ Storr, Wayne (2013-08-21). "Logic NOR Gate Tutorial with Logic NOR Gate Truth Table". Basic Electronics Tutorials. Retrieved 2025-10-31.

NOR logic

View on GrokipediaFundamentals

Definition and Functionality

In digital electronics, logic gates serve as the fundamental building blocks for constructing circuits that process binary signals, where information is represented using two distinct voltage levels: low (0, corresponding to false or off) and high (1, corresponding to true or on).[7] These gates perform specific Boolean operations on one or more input signals to produce a single output signal, enabling the implementation of complex computational functions in computers and other electronic devices.[8] The NOR gate, short for "NOT-OR," is a specific type of logic gate that outputs a high signal (1) only when all of its inputs are low (0); in all other cases, the output is low (0).[9] This behavior represents the logical negation of the OR operation, where the OR gate itself would output high (1) if at least one input is high, and the NOR inverts that result.[8] As such, the NOR gate effectively computes the complement of the inclusive OR function across its inputs, making it a versatile primitive in Boolean algebra.[10] NOR gates are not limited to two inputs and can be designed with three or more inputs, maintaining the same principle: the output remains high (1) exclusively when every single input is low (0), and drops to low (0) if any input is high.[11] This scalability allows NOR gates to handle multiple signals in integrated circuits, where the gate's output reflects the absence of activity across all inputs. For instance, consider a two-input NOR gate modeling a safety system, such as an alarm that activates (outputs 1) only if both sensors detect no intrusion (both inputs 0), remaining silent (output 0) if either sensor triggers.[9]Symbols and Circuit Representation

The standard graphical representation of a NOR gate follows the ANSI/IEEE Std 91-1984, which uses a distinctive curved shape resembling an OR gate—typically a concave arc with multiple input lines on the left side and output on the right side—combined with a small circular bubble at the output to indicate inversion.[12] This bubble, known as a negation qualifier, denotes that the output is the logical complement of the OR operation, transforming an active-high OR into an active-low NOR.[2] Alternative symbols include the IEC 60617 standard, which employs a rectangular box for the gate outline, with inputs on the left, an output on the right, and a circular inversion marker at the output; the interior may feature a ">1" notation to signify the OR function before negation. Historical variations encompass the older MIL-STD-806B military symbols, which are similar to the ANSI/IEEE distinctive shapes but with more rigid geometric constraints for schematic clarity in defense applications, and the obsolete DIN 40700 standard used in Germany, featuring a rectangular form akin to IEC.[13] At the circuit level, a two-input NOR gate in CMOS technology is implemented using four transistors: two p-channel MOSFETs (PMOS) connected in series between the power supply and output for the pull-up network, and two n-channel MOSFETs (NMOS) connected in parallel between the output and ground for the pull-down network.[14] In TTL implementations, the gate typically employs a multi-emitter bipolar junction transistor (BJT) for the inputs, followed by additional BJTs in a totem-pole configuration to drive the output, enabling efficient switching with standard 5V logic levels.[15] Symbols for NOR gates adhere to active-high conventions for inputs by default, where a logic high (typically 3.5–5V) asserts the signal without bubbles on input lines; however, the output bubble denotes the inversion of the OR function, resulting in a high output when the internal OR is false (all inputs low). In standard active-high logic, both inputs and output are active-high. Bubbles or triangular polarity indicators on inputs would denote active-low inputs, inverting the signal before processing, while such qualifiers ensure compatibility across positive and negative logic systems in mixed-signal designs.[16][17]Truth Table and Boolean Expression

The logical operation performed by a two-input NOR gate is specified by its truth table, which lists all possible combinations of input values and the resulting output. The table is as follows:| Input A | Input B | Output |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

Universality

Functional Completeness

Functional completeness refers to the property of a set of logical connectives that allows the expression of any arbitrary Boolean function using only combinations of those connectives.[24] In digital logic, a single gate type possesses functional completeness if it alone can implement all possible Boolean operations, thereby serving as a universal gate.[1] The NOR gate exhibits this property because it can generate the negation (NOT), conjunction (AND), and disjunction (OR) operations, which together form a functionally complete set.[25] To demonstrate this, consider the construction of each basic operation using NOR gates. The NOT operation is realized by connecting both inputs of a single NOR gate to the input signal :Comparison to NAND and Other Gates

NOR logic gates share functional completeness with NAND gates, both serving as universal building blocks for constructing any Boolean function, though NAND outputs a logic 1 unless all inputs are 1, in contrast to NOR's output of 1 only when all inputs are 0. This duality arises from De Morgan's laws, where NOR is the complement of OR and NAND is the complement of AND, enabling symmetric yet inverse behaviors in circuit design. In CMOS implementations, NOR gates typically favor pull-down networks, which can simplify designs for higher fan-ins due to parallel NMOS transistors, while NAND gates prefer pull-up networks with parallel PMOS for similar reasons, leading to trade-offs in area and speed. Propagation delays for NOR gates are often longer in high-fan-in scenarios because of series PMOS paths in the pull-up network, whereas NAND gates can exhibit different delay characteristics due to series NMOS in the pull-down; power consumption is comparable but varies with process technology.[27] The following table summarizes key comparisons between NOR, NAND, AND, and OR gates:| Gate Type | Universality | Input Count Efficiency | Common Uses |

|---|---|---|---|

| NOR | Yes | High for OR-like functions; scales well in pull-down CMOS | Memory cells (e.g., NOR flash), PLA decoders |

| NAND | Yes | High for AND-like functions; efficient in pull-up CMOS | Standard SSI logic, adders, multiplexers |

| AND | No | Low; requires inversion for completeness | Basic combinational logic, but not universal |

| OR | No | Low; limited without complements | Signal merging, but paired with NOT for universality |

Constructing Other Logic Gates

NOT, OR, and AND Gates

The NOT gate can be constructed using a single NOR gate by connecting one input to the input signal A and the other input to logic 0 (ground). The output is then , which inverts the input as required for a NOT gate.[30] An OR gate requires two NOR gates for implementation. The first NOR gate takes inputs A and B, producing an output of . This output is fed into the second NOR gate along with logic 0 on the other input, yielding . In circuit terms: NOR1 inputs are A and B; NOR2 inputs are the output of NOR1 and 0.[31] The AND gate is built using three NOR gates, applying De Morgan's theorem: . The first NOR gate inverts A by taking inputs A and 0, producing . The second NOR gate similarly inverts B, producing . The third NOR gate takes and as inputs, outputting . In circuit terms: NOR1 inputs are A and 0; NOR2 inputs are B and 0; NOR3 inputs are outputs of NOR1 and NOR2. These constructions demonstrate the minimal number of NOR gates needed: one for NOT, two for OR, and three for AND.[32] These basic gate constructions using NOR gates form the foundation for realizing any Boolean function, underscoring the functional completeness of the NOR gate in digital circuit design.[33]NAND and NOR Gates

To construct a NAND gate using only NOR gates, four two-input NOR gates are required. The first two NOR gates act as inverters to produce the complements of the inputs: and . These complemented signals are then fed into a third NOR gate, yielding . Finally, the output of this gate is inverted using a fourth NOR gate configured as a NOT: , which produces the NAND function.[33] This construction can be verified using De Morgan's theorem, which states that . The circuit effectively computes through the intermediate AND followed by inversion, equivalent to the direct disjunction of complements, confirming the NAND output for all input combinations (e.g., when and , the result is 0; otherwise, 1).[34] In contrast to basic gates like NOT (one NOR), OR (two NORs), and AND (three NORs), the NAND requires four NOR gates, underscoring a relative inefficiency in this decomposition but demonstrating NOR's versatility as a universal gate for compound functions.[33] The construction of a NOR gate from NOR gates is trivial, requiring only a single gate, as it is the primitive itself. This inclusion serves for completeness in discussions of universal gate sets, ensuring all standard logic operations can be systematically derived without assuming primitives beyond two-input NOR.[35] For multi-input NOR gates, such as a three- or four-input version, a single multi-input NOR primitive is often used in practice for efficiency. However, when restricted to two-input NOR gates, a tree structure can build the equivalent by first constructing a multi-input OR (via cascaded two-input OR subcircuits, each using two NORs) and then applying a final NOT using one NOR. For a four-input NOR, this requires three two-input ORs (six NORs) plus one NOT (one NOR), totaling seven gates, though optimized designs may reduce this in integrated circuits.[36]XOR and XNOR Gates

The XOR gate performs an exclusive disjunction operation, producing an output of 1 when its two inputs differ. Its Boolean expression is . This can be realized using five 2-input NOR gates in a multilevel circuit. The construction begins with a NOR gate taking inputs A and B to produce intermediate signal . A second NOR gate then takes A and P to yield , while a third NOR gate takes B and P to yield . A fourth NOR gate combines Q and R to produce , the XNOR output. Finally, a fifth NOR gate inverts S by feeding it to both inputs, yielding the XOR output . This NOR-based XOR circuit matches the standard truth table:| A | B | A ⊕ B |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |