Recent from talks

Nothing was collected or created yet.

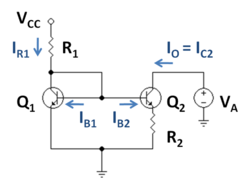

Widlar current source

View on Wikipedia

A Widlar current source is a modification of the basic two-transistor current mirror that incorporates an emitter degeneration resistor for only the output transistor, enabling the current source to generate low currents using only moderate resistor values.[1][2][3]

The Widlar circuit may be used with bipolar transistors, MOS transistors, and even vacuum tubes. An example application is the 741 operational amplifier,[4] and Widlar used the circuit as a part in many designs.[5]

This circuit is named after its inventor, Bob Widlar, and was patented in 1967.[6][7]

DC analysis

[edit]

Figure 1 is an example Widlar current source using bipolar transistors, where the emitter resistance R2 is connected to the output transistor Q2, and has the effect of reducing the current in Q2 relative to Q1. The key to this circuit is that the voltage drop across the resistance R2 subtracts from the base-emitter voltage of transistor Q2, thereby turning this transistor off compared to transistor Q1. This observation is expressed by equating the base voltage expressions found on either side of the circuit in Figure 1 as:

where β2 is the beta-value of the output transistor, which is not the same as that of the input transistor, in part because the currents in the two transistors are very different.[8] The variable IB2 is the base current of the output transistor, VBE refers to base-emitter voltage. This equation implies (using the Shockley diode equation):

Eq. 1

where VT is the thermal voltage.

This equation makes the approximation that the currents are both much larger than the scale currents, IS1 and IS2; an approximation valid except for current levels near cut off. In the following, the scale currents are assumed to be identical; in practice, this needs to be specifically arranged.

Design procedure with specified currents

[edit]To design the mirror, the output current must be related to the two resistor values R1 and R2. A basic observation is that the output transistor is in active mode only so long as its collector-base voltage is non-zero. Thus, the simplest bias condition for design of the mirror sets the applied voltage VA to equal the base voltage VB. This minimum useful value of VA is called the compliance voltage of the current source. With that bias condition, the Early effect plays no role in the design.[9]

These considerations suggest the following design procedure:

- Select the desired output current, IO = IC2.

- Select the reference current, IR1, assumed to be larger than the output current, probably considerably larger (that is the purpose of the circuit).

- Determine the input collector current of Q1, IC1:

- Determine the base voltage VBE1 using the Shockley diode law

- where IS is a device parameter sometimes called the scale current.

- The value of base voltage also sets the compliance voltage VA = VBE1. This voltage is the lowest voltage for which the mirror works properly.

- Determine R1:

- Determine the emitter leg resistance R2 using Eq. 1 (to reduce clutter, the scale currents are chosen equal):

Finding the current with given resistor values

[edit]The inverse of the design problem is finding the current when the resistor values are known. An iterative method is described next. Assume the current source is biased so the collector-base voltage of the output transistor Q2 is zero. The current through R1 is the input or reference current given as,

Rearranging, IC1 is found as:

Eq. 2

The diode equation provides:

Eq. 3

Eq.1 provides:

These three relations are a nonlinear, implicit determination for the currents that can be solved by iteration.

- We guess starting values for IC1 and IC2.

- We find a value for VBE1:

- We find a new value for IC1:

- We find a new value for IC2:

This procedure is repeated to convergence, and is set up conveniently in a spreadsheet. One simply uses a macro to copy the new values into the spreadsheet cells holding the initial values to obtain the solution in short order.

Note that with the circuit as shown, if VCC changes, the output current will change. Hence, to keep the output current constant despite fluctuations in VCC, the circuit should be driven by a constant current source rather than using the resistor R1.

Exact solution

[edit]The transcendental equations above can be solved exactly in terms of the Lambert W function.

Output impedance

[edit]

An important property of a current source is its small signal incremental output impedance, which should ideally be infinite. The Widlar circuit introduces local current feedback for transistor . Any increase in the current in Q2 increases the voltage drop across R2, reducing the VBE for Q2, thereby countering the increase in current. This feedback means the output impedance of the circuit is increased, because the feedback involving R2 forces use of a larger voltage to drive a given current.

Output resistance is found using a small-signal model for the circuit, shown in Figure 2. Transistor Q1 is replaced by its small-signal emitter resistance rE because it is diode connected.[10] Transistor Q2 is replaced with its hybrid-pi model. A test current Ix is attached at the output.

Using the figure, the output resistance is determined using Kirchhoff's laws. Using Kirchhoff's voltage law from the ground on the left to the ground connection of R2:

Rearranging:

Using Kirchhoff's voltage law from the ground connection of R2 to the ground of the test current:

or, substituting for Ib:

Eq. 4

According to Eq. 4, the output resistance of the Widlar current source is increased over that of the output transistor itself (which is rO) so long as R2 is large enough compared to the rπ of the output transistor (large resistances R2 make the factor multiplying rO approach the value (β + 1)). The output transistor carries a low current, making rπ large, and increase in R2 tends to reduce this current further, causing a correlated increase in rπ. Therefore, a goal of R2 ≫ rπ can be unrealistic, and further discussion is provided below. The resistance R1∥rE usually is small because the emitter resistance rE usually is only a few ohms.

Current dependence of output resistance

[edit]

The current dependence of the resistances rπ and rO is discussed in the article hybrid-pi model. The current dependence of the resistor values is:

and

is the output resistance due to the Early effect when VCB = 0 V (device parameter VA is the Early voltage).

From earlier in this article (setting the scale currents equal for convenience): Eq. 5

Consequently, for the usual case of small rE, and neglecting the second term in RO with the expectation that the leading term involving rO is much larger: Eq. 6

where the last form is found by substituting Eq. 5 for R2. Eq. 6 shows that a value of output resistance much larger than rO of the output transistor results only for designs with IC1 >> IC2. Figure 3 shows that the circuit output resistance RO is not determined so much by feedback as by the current dependence of the resistance rO of the output transistor (the output resistance in Figure 3 varies four orders of magnitude, while the feedback factor varies only by one order of magnitude).

Increase of IC1 to increase the feedback factor also results in increased compliance voltage, not a good thing as that means the current source operates over a more restricted voltage range. So, for example, with a goal for compliance voltage set, placing an upper limit upon IC1, and with a goal for output resistance to be met, the maximum value of output current IC2 is limited.

The center panel in Figure 3 shows the design trade-off between emitter leg resistance and the output current: a lower output current requires a larger leg resistor, and hence a larger area for the design. An upper bound on area therefore sets a lower bound on the output current and an upper bound on the circuit output resistance.

Eq. 6 for RO depends upon selecting a value of R2 according to Eq. 5. That means Eq. 6 is not a circuit behavior formula, but a design value equation. Once R2 is selected for a particular design objective using Eq. 5, thereafter its value is fixed. If circuit operation causes currents, voltages or temperatures to deviate from the designed-for values; then to predict changes in RO caused by such deviations, Eq. 4 should be used, not Eq. 6.

See also

[edit]References

[edit]- ^ PR Gray, PJ Hurst, SH Lewis & RG Meyer (2001). Analysis and design of analog integrated circuits (4th ed.). John Wiley and Sons. pp. §4.4.1.1 pp. 299–303. ISBN 0-471-32168-0.

{{cite book}}: CS1 maint: multiple names: authors list (link) - ^ AS Sedra & KC Smith (2004). Microelectronic circuits (5th ed.). Oxford University Press. Example 6.14, pp. 654–655. ISBN 0-19-514251-9.

- ^ MH Rashid (1999). Microelectronic circuits: analysis and design. PWS Publishing Co. pp. 661–665. ISBN 0-534-95174-0.

- ^ AS Sedra & KC Smith (2004). §9.4.2, p. 899 (5th ed.). ISBN 0-19-514251-9.

- ^ See, for example, Figure 2 in IC voltage regulators.

- ^ RJ Widlar: US Patent Number 03320439; Filed May 26, 1965; Granted May 16, 1967: Low-value current source for integrated circuits

- ^ See Widlar: Some circuit design techniques for linear integrated circuits and Design techniques for monolithic operational amplifiers

- ^ PR Gray, PJ Hurst, SH Lewis & RG Meyer (2001). Figure 2.38, p. 115. ISBN 0-471-32168-0.

{{cite book}}: CS1 maint: multiple names: authors list (link) - ^ Of course, one might imagine a design where the output resistance of the mirror is a major consideration. Then a different approach is necessary.

- ^ In a diode-connected transistor the collector is short-circuited to the base, so the transistor collector-base junction has no time-varying voltage across it. As a result, the transistor behaves like the base-emitter diode, which at low frequencies has a small-signal circuit that is simply the resistor rE = VT / IE, with IE the DC Q-point emitter current. See diode small-signal circuit.

Further reading

[edit]- Linden T. Harrison (2005). Current Sources and Voltage References: A Design Reference for Electronics Engineers. Elsevier-Newnes. ISBN 0-7506-7752-X.

- Sundaram Natarajan (2005). Microelectronics: Analysis and Design. Tata McGraw-Hill. p. 319. ISBN 0-07-059096-6.

- Current mirrors and active loads: Mu-Huo Cheng

![{\displaystyle {\begin{aligned}(\beta _{2}+1)I_{\text{B2}}&=\left(1+{\frac {1}{\beta _{2}}}\right)I_{\text{C2}}={\frac {1}{R_{2}}}\left(V_{\text{BE1}}-V_{\text{BE2}}\right)\\&={\frac {V_{\text{T}}}{R_{2}}}\left[\ln \left(I_{\text{C1}}/I_{\text{S1}}\right)-\ln \left(I_{\text{C2}}/I_{\text{S2}}\right)\right]={\frac {V_{\text{T}}}{R_{2}}}\ln \left({\frac {I_{\text{C1}}I_{\text{S2}}}{I_{\text{C2}}I_{\text{S1}}}}\right)\ ,\end{aligned}}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/80e397e1ca48954365337e9751eeb2b6c26bf4fc)

![{\displaystyle I_{\text{b}}\left[(R_{1}\parallel r_{\text{E}})+r_{\pi }\right]+[I_{\text{x}}+I_{\text{b}}]R_{2}=0\ .}](https://wikimedia.org/api/rest_v1/media/math/render/svg/bf96d066bd22bb7dd7cd628cb24d2120a4c31806)

![{\displaystyle R_{\text{O}}={\frac {V_{\text{x}}}{I_{\text{x}}}}=r_{\text{O}}\left[1+{\frac {\beta R_{2}}{(R_{1}\parallel r_{\text{E}})+r_{\pi }+R_{2}}}\right]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/bf90a801fb3380f917699378ca418d4bbf7b732b)

![{\displaystyle +\ R_{2}\left[{\frac {(R_{1}\parallel r_{\text{E}})+r_{\pi }}{(R_{1}\parallel r_{\text{E}})+r_{\pi }+R_{2}}}\right]\ .}](https://wikimedia.org/api/rest_v1/media/math/render/svg/9fffd04ee8fff77ab87020199fe791b7207293c5)