Recent from talks

Nothing was collected or created yet.

Programmable logic device

View on Wikipedia

A programmable logic device (PLD) is an electronic component used to build reconfigurable digital circuits. Unlike digital logic constructed using discrete logic gates with fixed functions, the function of a PLD is undefined at the time of manufacture. Before the PLD can be used in a circuit it must be programmed to implement the desired function.[1] Compared to fixed logic devices, programmable logic devices simplify the design of complex logic and may offer superior performance.[2] Unlike for microprocessors, programming a PLD changes the connections made between the gates in the device.

PLDs can broadly be categorised into, in increasing order of complexity, simple programmable logic devices (SPLDs), comprising programmable array logic, programmable logic array and generic array logic; complex programmable logic devices (CPLDs); and field-programmable gate arrays (FPGAs).

History

[edit]In 1969, Motorola offered the XC157, a mask-programmed gate array with 12 gates and 30 uncommitted input/output pins.[3]

In 1970, Texas Instruments developed a mask-programmable IC based on the IBM read-only associative memory or ROAM. This device, the TMS2000, was programmed by altering the metal layer during the production of the IC. The TMS2000 had up to 17 inputs and 18 outputs with 8 JK flip-flops for memory. TI coined the term programmable logic array (PLA) for this device.[4]

In 1971, General Electric Company (GE) was developing a programmable logic device based on the new programmable read-only memory (PROM) technology. This experimental device improved on IBM's ROAM by allowing multilevel logic. Intel had just introduced the floating-gate UV EPROM so the researcher at GE incorporated that technology. The GE device was the first erasable PLD ever developed, predating the Altera EPLD by over a decade. GE obtained several early patents on programmable logic devices.[5][6][7]

In 1973 National Semiconductor introduced a mask-programmable PLA device (DM7575) with 14 inputs and 8 outputs with no memory registers. This was more popular than the TI part but the cost of making the metal mask limited its use. The device is significant because it was the basis for the field programmable logic array produced by Signetics in 1975, the 82S100. (Intersil actually beat Signetics to market but poor yield doomed their part.)[8][9]

In 1974 GE entered into an agreement with Monolithic Memories (MMI) to develop a mask-programmable logic device incorporating the GE innovations. The device was named programmable associative logic array or PALA. The MMI 5760 was completed in 1976 and could implement multilevel or sequential circuits of over 100 gates. The device was supported by a GE design environment where Boolean equations would be converted to mask patterns for configuring the device. The part was never brought to market.[10]

PLA

[edit]In 1970, Texas Instruments developed a mask-programmable IC based on the IBM read-only associative memory or ROAM. This device, the TMS2000, was programmed by altering the metal layer during the production of the IC. The TMS2000 had up to 17 inputs and 18 outputs with 8 JK flip-flops for memory. TI coined the term programmable logic array for this device.[4]

A programmable logic array (PLA) has a programmable AND gate array, which links to a programmable OR gate array, which can then be conditionally complemented to produce an output. A PLA is similar to a ROM concept; however, a PLA does not provide full decoding of a variable and does not generate all the minterms as in a ROM.

The programmable logic sequencer (PLS/FPLS) is similar to a PLA, but with integral registered outputs using a number of flip-flops to allow creation of some state machines. Signetics introduced the first FPLS in 1979.[11]

PAL

[edit]PAL devices have arrays of transistor cells arranged in a "fixed-OR, programmable-AND" plane used to implement "sum-of-products" binary logic equations for each of the outputs in terms of the inputs and either synchronous or asynchronous feedback from the outputs.

MMI introduced a breakthrough device in 1978, the programmable array logic or PAL. The architecture was simpler than that of Signetics' FPLA because it omitted the programmable OR array. This made the parts faster, smaller and cheaper. They were available in 20-pin 300-mil DIP packages, while the FPLAs came in 28-pin 600-mil packages. The PAL Handbook demystified the design process. The PALASM design software (PAL assembler) converted the engineers' Boolean equations into the fuse pattern required to program the part. The PAL devices were soon second-sourced by National Semiconductor, Texas Instruments and AMD.

After MMI succeeded with the 20-pin PAL parts, AMD introduced the 24-pin 22V10 PAL with additional features. After buying out MMI (1987), AMD spun off a consolidated operation as Vantis, and that business was acquired by Lattice Semiconductor in 1999.

GALs

[edit]

An improvement on the PAL was the generic array logic device, or GAL, invented by Lattice Semiconductor in 1985. This device has the same logical properties as the PAL but can be erased and reprogrammed. The GAL is very useful in the prototyping stage of a design when any bugs in the logic can be corrected by reprogramming. GALs are programmed and reprogrammed using a PAL programmer, or, in the case of chips that support it, by using the in-circuit programming technique.

Lattice GALs combine CMOS and electrically erasable (E2) floating gate technology for a high-speed, low-power logic device. A similar device called a PEEL (programmable electrically erasable logic) was introduced by the International CMOS Technology (ICT) corporation.

Sometimes GAL chips are referred as simple programmable logic device (SPLD), analogous to complex programmable logic device (CPLD) below.

CPLDs

[edit]PALs and GALs are available only in small sizes, equivalent to a few hundred logic gates. For bigger logic circuits, complex PLDs or CPLDs can be used. These contain the equivalent of several PALs linked by programmable interconnections, all in one integrated circuit. CPLDs can replace thousands, or even hundreds of thousands, of logic gates.

Some CPLDs are programmed using a PAL programmer, but this method becomes inconvenient for devices with hundreds of pins. A second method of programming is to solder the device to its printed circuit board, then feed it with a serial data stream from a personal computer. The CPLD contains a circuit that decodes the data stream and configures the CPLD to perform its specified logic function. Some manufacturers, such as Altera and Atmel (now Microchip), use JTAG to program CPLDs in-circuit from .JAM files.

FPGAs

[edit]While PALs were being developed into GALs and CPLDs (all discussed above), a separate stream of development was happening. This type of device is based on gate array technology and is called the field-programmable gate array (FPGA). Early examples of FPGAs are the 82S100 array and 82S105 sequencer, by Signetics, introduced in the late 1970s. The 82S100 was an array of AND terms. The 82S105 also had flip-flop functions.

(Remark: 82S100 and similar ICs from Signetics have PLA structure, AND-plane + OR-plane.)

FPGAs use a grid of logic gates, and once stored, the data doesn't change, similar to that of an ordinary gate array. The term field-programmable means the device is programmed by the customer, not the manufacturer. FPGAs and gate arrays are similar but gate arrays can only be configured at the factory during fabrication.[12][13][14]

FPGAs are usually programmed after being soldered down to the circuit board, in a manner similar to that of larger CPLDs. In most larger FPGAs, the configuration is volatile and must be re-loaded into the device whenever power is applied or different functionality is required. Configuration is typically stored in a configuration PROM, EEPROM or flash memory.[15] EEPROM versions may be in-system programmable (typically via JTAG).

The difference between FPGAs and CPLDs is that FPGAs are internally based on look-up tables (LUTs), whereas CPLDs form the logic functions with sea-of-gates (e.g. sum of products). CPLDs are meant for simpler designs, while FPGAs are meant for more complex designs. In general, CPLDs are a good choice for wide combinational logic applications, whereas FPGAs are more suitable for large state machines such as microprocessors.

EPLDs

[edit]

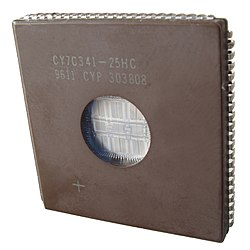

Using the same technology as EPROMs, EPLDs have a quartz window in the package that allows them to be erased on exposure to UV light.[16][17]

Using the same technology as EEPROMs, EEPLDs can be erased electrically.[16][17]

An erasable programmable logic device (EPLD) is an integrated circuit that comprises an array of PLDs that do not come pre-connected; the connections are programmed electrically by the user. Most GAL and FPGA devices are examples of EPLDs.[citation needed]

Other variants

[edit]These are microprocessor circuits that contain some fixed functions and other functions that can be altered by code running on the processor. Designing self-altering systems requires that engineers learn new methods and that new software tools be developed.

PLDs are being sold now that contain a microprocessor with a fixed function (the so-called core) surrounded by programmable logic. These devices let designers concentrate on adding new features to designs without having to worry about making the microprocessor work. Also, the fixed-function microprocessor takes less space on the chip than a part of the programmable gate array implementing the same processor, leaving more space for the programmable gate array to contain the designer's specialized circuits.

How PLDs retain their configuration

[edit]A PLD is a combination of a logic device and a memory device. The memory is used to store the pattern that was given to the chip during programming. Most of the methods for storing data in an integrated circuit have been adapted for use in PLDs. These include:

Silicon antifuses are connections that are made by applying a voltage across a modified area of silicon inside the chip. They are called antifuses because they work in the opposite way to normal fuses, which begin life as connections until they are broken by an electric current.

SRAM, or static RAM, is a volatile type of memory, meaning that its contents are lost each time the power is switched off. SRAM-based PLDs therefore have to be programmed every time the circuit is switched on. This is usually done automatically by another part of the circuit.

An EPROM memory cell is a MOSFET (metal-oxide-semiconductor field-effect transistor, or MOS transistor) that can be switched on by trapping an electric charge permanently on its gate electrode. This is done by a PAL programmer. The charge remains for many years and can only be removed by exposing the chip to strong ultraviolet light in a device called an EPROM eraser.

Flash memory is non-volatile, retaining its contents even when the power is switched off. It is stored on floating-gate MOSFET memory cells, and can be erased and reprogrammed as required. This makes it useful in PLDs that may be reprogrammed frequently, such as PLDs used in prototypes. Flash memory is a kind of EEPROM that holds information using trapped electric charges similar to EPROM. Consequently, flash memory can hold information for years, but possibly not as many years as EPROM.

As of 2005, most CPLDs are electrically programmable and erasable, and non-volatile. This is because they are too small to justify the inconvenience of programming internal SRAM cells every time they start up, and EPROM cells are more expensive due to their ceramic package with a quartz window.

PLD programming languages

[edit]Many PAL programming devices accept input in a standard file format, commonly referred to as 'JEDEC files'. They are analogous to software compilers. The languages used as source code for logic compilers are called hardware description languages, or HDLs.[1]

PALASM, ABEL and CUPL are frequently used for low-complexity devices, while Verilog and VHDL are popular higher-level description languages for more complex devices. The more limited ABEL is often used for historical reasons, but for new designs, VHDL is more popular, even for low-complexity designs.

For modern PLD programming languages, design flows, and tools, see FPGA and reconfigurable computing.

PLD programming devices

[edit]A device programmer is used to transfer the Boolean logic pattern into the programmable device. In the early days of programmable logic, every PLD manufacturer also produced a specialized device programmer for its family of logic devices. Later, universal device programmers came onto the market that supported several logic device families from different manufacturers. Today's device programmers usually can program common PLDs (mostly PAL/GAL equivalents) from all existing manufacturers. Common file formats used to store the Boolean logic pattern (fuses) are JEDEC, Altera POF (programmable object file), or Xilinx BITstream.[18]

See also

[edit]References

[edit]- ^ a b Horowitz, Paul; Hill, Winfield (2015). Horowitz P., Hill W. - The Art of Electronics. New York. p. 764. ISBN 978-0-521-80926-9.

{{cite book}}: CS1 maint: location missing publisher (link) - ^ Holdsworth, B.; Woods, R. C. (2003). Digital Logic Design (4th ed.). Elsevier. ISBN 978-0-7506-4582-9.

- ^ Motorola Semiconductor Data Book, Fourth Edition. Motorola Inc. 1969. p. IC-73.

- ^ a b Andres, Kent (October 1970). A Texas Instruments Application Report: MOS programmable logic arrays. Texas Instruments. Bulletin CA-158. Report introduces the TMS2000 and TMS2200 series of mask programmable PLAs.

- ^ Greer, David L. Electrically Programmable Logic Circuits US Patent 3,818,452. Assignee: General Electric, Filed: April 28, 1972, Granted: June 18, 1974

- ^ Greer, David L. Multiple Level Associative Logic Circuits US Patent 3,816,725. Assignee: General Electric, Filed: April 28, 1972, Granted: June 11, 1974

- ^ Greer, David L. Segmented Associative Logic Circuits US Patent 3,849,638. Assignee: General Electric, Filed: July 18, 1973, Granted: November 19, 1974

- ^ "Semiconductors and IC's : FPLA". EDN. 20 (13). Boston, MA: Cahners Publishing: 66. July 20, 1975. Press release on Intersil IM5200 field programmable logic array. Fourteen inputs pins and 48 product terms. Avalanched-induced-migration programming. Unit price was $37.50

- ^ "FPLA's give quick custom logic". EDN. 20 (13). Boston, MA: Cahners Publishing: 61. July 20, 1975. Press release on Signetics 82S100 and 82S101 field programmable logic arrays. Fourteen inputs pins, 8 output pins and 48 product terms. NiCr fuse link programming.

- ^ Pellerin, David; Michael Holley (1991). Practical Design Using Programmable Logic. Prentice-Hall. p. 15. ISBN 0-13-723834-7.

- ^ Alford, Roger C. (1989). Programmable Logic Designer's Guide. Howard W. Sams. pp. 67–69. ISBN 0-672-22575-1.

The registers can be dynamically or permanently configured as D, J-K, or T flip-flops, because of the flexibility offered by the inclusion of the "M" inverters (M0-M5). The outputs of the registers are fed back into the AND-array before reaching the tri-state output buffers, allowing for Mealy and Moore state machine development.

- ^ Dorf, Richard C. (3 October 2018). Electronics, Power Electronics, Optoelectronics, Microwaves, Electromagnetics, and Radar. CRC Press. ISBN 978-1-4200-0315-4.

- ^ Vahid, Frank; Givargis, Tony D. (17 October 2001). Embedded System Design: A Unified Hardware / Software Introduction. John Wiley & Sons. ISBN 978-0-471-38678-0.

- ^ Chen, Wai-Kai (3 October 2018). The VLSI Handbook. CRC Press. ISBN 978-1-4200-0596-7.

- ^ "Using Flash Memory to Configure FPGAs" (PDF). Altera. Retrieved 2024-08-21.

- ^ a b Tertulien Ndjountche. "Digital Electronics 2: Sequential and Arithmetic Logic Circuits". 2016. p. 224.

- ^ a b Clive Maxfield. "The Design Warrior's Guide to FPGAs". 2004. p. 20

- ^ PLD File Formats

External links

[edit]- "PLD Tools Creating SVF, JAM, STAPL and other formats". JTAG / boundary-scan. Corelis. Dec 1, 2010. Archived from the original on March 18, 2012. Retrieved July 18, 2011.

- "FPGAs and CPLDs". Lattice Semiconductor.

Programmable logic device

View on GrokipediaFundamentals

Definition and Principles

A programmable logic device (PLD) is an integrated circuit that can be configured by the user after manufacturing to implement specific digital logic functions, enabling the creation of custom combinational and sequential circuits on a single chip. Unlike application-specific integrated circuits (ASICs), which have fixed functionality defined during fabrication and are suited for high-volume production, PLDs offer post-production programmability, making them ideal for flexible designs where requirements may evolve. This reconfigurability is achieved through electronic programming mechanisms, such as SRAM-based configuration memory that loads logic definitions on power-up or non-volatile antifuse links that permanently set connections.[3][4] At their core, PLDs operate on principles of Boolean logic implementation, where user-defined functions are realized through programmable interconnects and logic elements that map inputs to outputs based on specified truth tables or equations. Combinational logic is supported by structures that compute instantaneous outputs solely from current inputs, often using sum-of-products forms involving programmable AND and OR planes or lookup tables (LUTs) that store precomputed results for small input sets (e.g., a 4-input LUT with 16 entries). Sequential logic extends this by incorporating memory elements like flip-flops to retain state, allowing outputs to depend on both current inputs and prior states, thus enabling finite state machines and registers. The granularity of PLDs ranges from basic gate-level equivalents to higher-level system functions, accommodating designs from simple glue logic to complex subsystems.[5][3][4] Key advantages of PLDs stem from their reconfigurability, which facilitates rapid prototyping, cost-effective low-volume production, and in-field updates without hardware replacement, reducing time-to-market and development costs compared to custom silicon. Device density is typically measured in equivalent logic gates or configurable cells, scaling from hundreds in simpler devices to millions in advanced ones, reflecting the computational capacity and complexity they can handle. A generic block diagram of a PLD consists of an array of programmable logic blocks—each capable of implementing basic functions—interconnected by a network of programmable switches that route signals dynamically, with input/output pins interfacing to external systems.[4][5]Basic Architecture and Operation

Programmable logic devices (PLDs) feature architectures that vary by type but generally include programmable logic blocks for implementing user-defined functions, extensive programmable interconnect resources for signal routing, and input/output (I/O) blocks for external interfacing. In simpler PLDs like programmable logic arrays (PLAs) and programmable array logic (PALs), logic is realized using an AND array to generate product terms from inputs and their complements, and an OR array to sum selected terms, enabling sum-of-products (SOP) expressions. More complex devices, such as field-programmable gate arrays (FPGAs), employ configurable logic blocks (CLBs) that utilize lookup tables (LUTs) to implement arbitrary combinational functions by addressing precomputed truth table values, often combined with multiplexers for efficient routing within the block.[6][7][8] Programmable logic elements, such as macrocells in simple and complex PLDs or slices within CLBs in FPGAs, serve as the fundamental building blocks for both combinational and sequential logic. These elements typically integrate combinational logic outputs with optional flip-flops for state storage, along with features like XOR gates for output polarity control and configurable paths for direct combinational outputs. Detailed architectures of macrocells and CLBs are covered in sections on specific PLD types. I/O blocks manage external connections, incorporating tri-state buffers that allow pins to operate in input (high-impedance), output (driving), or bidirectional modes, while providing buffering to meet load and signaling standards.[6][7] In operation, PLDs are configured using technologies such as one-time programmable fuses or antifuses (blown via high current or dielectric breakdown), non-volatile EPROM/EEPROM/Flash cells (programmed electrically and erasable via UV or electrical means), or volatile SRAM (requiring reconfiguration on each power-up). This configuration defines the logic functions and interconnections: for array-based designs, inputs are decoded to form product terms (e.g., ) in the AND plane, which are then ORed to produce outputs; in LUT-based designs, inputs select entries from the table to compute functions directly. For combinational logic in SOP form, the expression is where the sum selects programmed product terms, with literals derived from inputs. LUTs generalize this by storing any function for their input width. Sequential operation involves clocked flip-flops (typically D-type) for state retention, with global or local clocks ensuring synchronous timing across elements.[6][7][5] Signal flow in PLDs proceeds from input decoding and logic evaluation in the programmable blocks, through interconnect routing, to processing in logic elements, and finally to output buffering in I/O blocks, where tri-state controls manage bus access. Power consumption includes static leakage in memory elements and dynamic switching in logic and routing, while performance is influenced by propagation delays in gates and interconnects, which have decreased significantly with advances in CMOS technology.[6]Historical Development

Origins and Early Innovations

The origins of programmable logic devices (PLDs) trace back to the early 1970s, building on the introduction of programmable read-only memories (PROMs) around 1970 by companies like Texas Instruments and Radiation Inc., which provided a foundation for configurable digital logic.[9] PROMs allowed users to program memory contents in the field using fuse-blowing techniques, inspiring designers to adapt similar concepts for logic implementation amid the rising complexity and cost of custom application-specific integrated circuits (ASICs). This need arose as TTL-based boards required replacing numerous discrete random logic gates with more efficient, flexible alternatives to reduce board space and design time.[9] A key innovation came in 1970 with Texas Instruments' development of the first programmable logic array (PLA), the TMS2000, a mask-programmable integrated circuit based on IBM's read-only associative memory (ROAM) technology. The TMS2000 featured an AND-OR array structure capable of implementing combinational and sequential logic, with up to 17 inputs, 18 outputs, and 8 JK flip-flops for state storage, marking the shift from pure memory to programmable logic functions. Early PLAs like this focused on streamlining random logic in TTL systems but faced challenges such as high manufacturing costs, limited density (typically 16-48 inputs), and one-time mask programmability during manufacturing, or later irreversible fuse blowing in field-programmable variants, which restricted revisions and scalability.[2] In 1975, Monolithic Memories Inc. (MMI) advanced the field with the invention of the programmable array logic (PAL) device by engineers John Birkner and H.T. Chua, leveraging bipolar PROM technology for higher speeds compared to earlier MOS-based designs. PALs simplified the PLA architecture by fixing the OR array while keeping the AND array programmable, enabling faster prototyping of glue logic to replace multiple TTL chips on circuit boards. Despite these innovations, early PLDs remained expensive and density-limited, often supporting only small-scale functions, yet they laid the groundwork for field-configurable logic by addressing the inefficiencies of custom silicon in rapidly evolving digital systems.[10][11]Key Milestones and Commercialization

The 1980s marked a pivotal shift in programmable logic devices (PLDs) toward reprogrammable and CMOS-based architectures, addressing limitations of earlier fuse-based PLA and PAL devices that required physical replacement for reconfiguration. In 1985, Lattice Semiconductor introduced the Generic Array Logic (GAL) family, the first commercially successful electrically erasable PLDs using EEPROM technology for in-system reprogrammability without ultraviolet erasure, enabling faster design iterations and broader adoption in prototyping.[12] Shortly thereafter, in 1984, Altera Corporation launched the EP300, the industry's first erasable PLD (EPLD) built on CMOS technology, which significantly reduced power consumption compared to bipolar predecessors and facilitated integration into battery-powered and high-density applications.[9] These innovations overcame the one-time programmability of early PLDs, spurring commercial growth by allowing engineers to test and modify logic without hardware swaps.[13] The late 1980s and 1990s saw the commercialization of more complex PLD architectures, driven by the invention of field-programmable gate arrays (FPGAs) and complex PLDs (CPLDs). Xilinx, founded in 1984, released the XC2064 in 1985, the first FPGA, which supported larger, user-configurable logic designs through an array of configurable logic blocks and programmable interconnects, revolutionizing custom circuit development for volumes under 50,000 units.[14] In the 1990s, CPLDs gained traction with Xilinx's XC9500 series, introduced around 1996, offering non-volatile flash-based storage, in-system programmability, and densities up to thousands of gates, ideal for glue logic in embedded systems.[15] Market drivers included the widespread shift to CMOS processes for significantly lower static power dissipation—EPLDs and GALs consumed much less power than bipolar equivalents—and the integration of PC-based design tools, such as Lattice's GAL Programmer software released in the mid-1980s, which allowed logic synthesis and simulation directly on IBM PCs, democratizing PLD development.[9] By 2000, the MOS logic IC sector had reached $31 billion, with PLDs contributing to its growth through adoption in telecommunications, computing, and consumer electronics.[16] Key corporate events further shaped PLD commercialization. In 1999, Lattice Semiconductor acquired Vantis Corporation from AMD for $500 million, gaining advanced SRAM-based FPGA technology and strengthening its position in high-density reprogrammable logic.[17] This consolidation helped Lattice expand its portfolio amid growing competition. In 2015, Intel completed its $16.7 billion acquisition of Altera, integrating PLD expertise into its data center and AI ecosystems; as of 2025, this merger continues to influence PLD evolution through enhanced software tools and silicon integration, boosting market penetration in high-performance computing.[18]Simple Programmable Logic Devices

Programmable Logic Array (PLA)

The Programmable Logic Array (PLA) represents the foundational type of simple programmable logic device, introduced in the early 1970s as a mask-programmable integrated circuit by Texas Instruments, enabling flexible realization of combinational logic functions through two fully programmable logic levels.[19] Its core architecture features a programmable AND plane, which generates product terms (minterms) by selectively connecting inputs and their complements to fixed AND gates, followed by a programmable OR plane that combines these product terms to produce outputs, thereby supporting arbitrary sum-of-products (SOP) or product-of-sums (POS) expressions without restrictions on logic complexity.[20] PLAs were fabricated using bipolar technology for high-speed applications or CMOS for lower power, with representative densities in the 1970s and 1980s typically accommodating 16 to 32 inputs, up to 72 product terms, and 8 to 16 outputs, making them suitable for implementing state machines, sequencers, and control logic in digital systems during that period.[8] Programming in early bipolar PLAs relied on fuse-based mechanisms, where metallic fuses were selectively blown via electrical pulses to establish connections in the AND and OR planes for one-time configuration, while later CMOS variants employed floating-gate transistors for non-volatile, reprogrammable storage.[21] Despite their versatility, PLAs exhibit limitations such as increased physical size and propagation delays compared to devices with fixed planes, owing to the dense interconnects required for dual-array programmability, which also contributed to higher power dissipation in bipolar implementations.[22]Programmable Array Logic (PAL)

Programmable Array Logic (PAL) devices, introduced by Monolithic Memories Inc. (MMI) in 1978, represent an optimized class of simple programmable logic devices (SPLDs) designed for high-speed implementation of combinational and simple sequential logic functions.[23] Unlike the more versatile programmable logic array (PLA), PAL prioritizes speed and density by employing a programmable AND array feeding into a fixed OR array, at the expense of some flexibility in OR-plane customization.[24] The core architecture of a PAL features a programmable AND plane composed of fusible links that allow selected input signals and their complements to form product terms, which are routed to a fixed OR array to produce sum-of-products outputs.[24] Each output connects to a macrocell, which includes a D-type flip-flop configurable for registered operation, along with feedback multiplexers to support sequential logic and state storage.[25] This design enables efficient realization of up to several dozen product terms per device, with bidirectional I/O pins enhancing pin utilization for both inputs and outputs.[24] PAL devices exhibit high performance, with propagation delays typically in the 10-25 ns range, achieved through bipolar TTL fabrication using Schottky processes for reduced switching times.[24] Standard configurations use 20- or 24-pin DIP packages, supporting 10-22 inputs and a similar number of outputs; the PAL20L8, for example, provides 10 dedicated inputs and 8 programmable outputs with three-state capability.[25] Programming occurs via a one-time fuse-blowing process, where high-current pulses sever selected links in the AND array using compatible PROM programmers.[24] Software tools like CUPL (Compiler for Universal Programmable Logic) enable design entry through Boolean equations, which are compiled into fuse patterns for direct device configuration, streamlining the implementation of custom logic.[25] During their peak era, PALs found widespread use as glue logic on microcomputer boards, interfacing microprocessors with memory, peripherals, and buses through functions like address decoding and control signal generation.[24] MMI and AMD collectively developed numerous variants, including speed grades, low-power options, and expanded I/O configurations, with early handbooks documenting over two dozen family members that evolved into broader offerings.[24][25]Generic Array Logic (GAL)

Generic Array Logic (GAL) devices represent an erasable evolution of Programmable Array Logic (PAL) structures, introduced by Lattice Semiconductor in 1985 to address the one-time programmability limitation of traditional bipolar PALs.[26] These devices employ electrically erasable and programmable read-only memory (EEPROM) technology, specifically Lattice's E²CMOS process, enabling multiple reprogramming cycles without requiring physical replacement.[26] This innovation allowed designers to iterate logic functions iteratively during development, significantly reducing prototyping costs and time compared to fuse-based PALs.[27] The architecture of GAL mirrors that of PAL in its core AND/OR array configuration but replaces the fixed fusible links in the AND array with floating-gate EEPROM cells, while the OR array remains fixed.[26] Erasure is achieved electronically through high-voltage pulses applied via standard programming equipment, completing in less than 100 milliseconds, followed by reprogramming without ultraviolet exposure or special handling.[26] Output Logic Macrocells (OLMCs) provide configurable modes—such as registered, combinatorial, or complex—for flexible logic implementation, with each macrocell supporting variable product terms (e.g., up to 10 terms per output in some configurations).[26] This design ensures pin-for-pin compatibility with PAL devices, facilitating drop-in replacements.[28] Key characteristics include operation at a 5 V supply voltage, with programming requiring a higher VPP of approximately 9 V for erasure and writing, and a guaranteed endurance of at least 100 erase/write cycles per cell, alongside 20-year data retention.[26][29] A representative example is the GAL16V8, a 20-pin device released in 1985 that emulates PAL16L8 and PAL16R8 functions, featuring eight OLMCs, propagation delays as low as 3.5 ns, and typical power consumption of 75 mA.[26][28] These attributes enable high-speed operation up to 250 MHz system frequency in optimized designs.[28] The primary advantages of GAL lie in its cost-effective support for design iteration, as reprogramming avoids the expense of new devices, and its role as a precursor to in-system programming (ISP) techniques in later PLDs.[27] Additionally, GAL incorporates security features, such as a programmable security cell that locks the fuse map to prevent unauthorized reading or copying, erasable only through full reprogramming.[26] This combination of erasability, compatibility, and protection made GAL a cornerstone for simple logic replacement in embedded systems during the late 1980s and 1990s.[26]Complex and Erasable PLDs

Erasable Programmable Logic Device (EPLD)

The Erasable Programmable Logic Device (EPLD), introduced by Altera in 1984, represents an early CMOS-based advancement in programmable logic, enabling UV-erasable, non-volatile reconfiguration to bridge the gap between simple fixed-architecture devices and more intricate designs. These devices utilized EPROM or EEPROM cells for storage, allowing erasure through ultraviolet light exposure typically requiring 30 minutes to 2 hours, which facilitated iterative prototyping without electrical reprogramming hardware. Unlike prior bipolar technologies, EPLDs offered significantly lower power consumption—often less than 40% of equivalent bipolar devices—while achieving higher integration densities suitable for replacing multiple TTL components.[30] At their core, EPLD architectures comprised multiple programmable array logic (PAL)-like blocks, known as logic array blocks (LABs), interconnected via a global programmable interconnect array (PIA) for flexible signal routing across the device. Each LAB contained macrocells with configurable AND/OR arrays, supporting up to 192 or more macrocells per device, enabling complex combinational and sequential logic implementations. For instance, Altera's MAX 7000 series, prominent in the 1990s, delivered densities up to 5,000 gates with propagation delays as low as 15 ns, making them viable for applications like address decoding and state machines.[30] Programming of EPLDs relied on standard JEDEC files generated by tools such as MAX+PLUS II, which compiled designs into fusemap data for in-circuit or off-circuit loading via dedicated programmers. Macrocells could be programmed as D-type, T-type, JK, or SR flip-flops, or purely combinatorial, with support for up to 256 macrocells in advanced configurations to handle expanded input/output requirements. Building briefly on the reprogrammability pioneered in devices like Lattice's GALs, EPLDs extended this capability through CMOS scalability for broader I/O and density, though relying on UV erasure rather than electrical methods.[30] As programmable logic evolved, EPLDs served as direct precursors to complex PLDs (CPLDs), influencing architectures with enhanced interconnects, but were phased out by the early 2000s in favor of electrically erasable, flash-based alternatives like Altera's MAX II series introduced in 2004, which eliminated the need for UV exposure and improved reconfiguration speed. By the 2010s, classic EPLDs were declared obsolete, with legacy support limited to existing inventories.[31]Complex Programmable Logic Device (CPLD)

Complex programmable logic devices (CPLDs) represent an evolution from erasable programmable logic devices (EPLDs) by integrating multiple arrays of macrocells with a centralized programmable interconnect array (PIA) to enable larger-scale designs while maintaining predictable performance.[8] The core architecture typically consists of 4 to 16 logic array blocks (LABs), each containing PAL- or GAL-like macrocells that implement combinational and sequential logic functions through configurable AND-OR planes and flip-flops. These macrocells are interconnected via the PIA, a switch matrix that routes signals between LABs, inputs, outputs, and buried nodes using non-volatile memory elements such as flash or EEPROM, allowing instant-on operation without external configuration memory. This fixed interconnect structure ensures low propagation delays and reliable timing, as the routing paths are determined at configuration time and do not require dynamic reconfiguration.[8] CPLDs offer logic densities ranging from approximately 600 to 10,000 usable gates, making them suitable for mid-scale applications where speed and power efficiency are prioritized over extreme flexibility.[32] Their non-volatile nature eliminates reconfiguration delays, enabling fast pin-to-pin logic delays as low as a few nanoseconds, which is advantageous in systems requiring immediate functionality upon power-up. For instance, Xilinx's CoolRunner family, introduced in the early 2000s, emphasized ultra-low power consumption with standby currents under 100 μA, targeting portable and remote applications through its Fast Zero Power (FZP) architecture.[33] Similarly, Altera's MAX II series, launched in 2004, utilized a flash-based process to deliver non-volatile CPLDs with up to 2,210 logic elements and reduced power compared to prior generations, achieving up to 50% lower total power in competitive benchmarks. Modern iterations, such as Intel's MAX 10 series introduced in 2014, extend these capabilities with higher densities and integrated features like analog-to-digital converters while preserving CPLD predictability.[34][35] The design flow for CPLDs focuses on partitioning user logic to fit within the fixed macrocell and PIA resources, using synthesis tools to map hardware description language (HDL) code into the device's AND-OR array structure. Timing closure is achieved through static analysis, where tools simulate propagation delays across predefined paths without simulation-based verification, ensuring compliance with clock and setup/hold requirements due to the architecture's inherent predictability. In telecommunications, CPLDs are commonly employed for glue logic to interface components, providing reliable signal routing and control without the overhead of more complex devices.[8]Field-Programmable Gate Arrays

Core Architecture

The core architecture of a field-programmable gate array (FPGA) consists of a two-dimensional array of configurable logic blocks (CLBs) interconnected by programmable routing resources and surrounded by input/output blocks (IOBs). Each CLB serves as the fundamental unit for implementing user-defined logic and storage, typically comprising multiple basic logic elements (BLEs) that include look-up tables (LUTs) for combinational functions and flip-flops for sequential elements. This island-style layout enables massive parallelism and scalability, distinguishing FPGAs from earlier programmable logic devices like complex programmable logic devices (CPLDs), which rely on fixed macrocell arrays rather than a flexible grid of independent blocks.[36] Within a CLB, LUTs form the primary logic elements, each capable of implementing any Boolean function of 4 to 6 inputs by storing the truth table in SRAM bits; for an n-input LUT, the capacity is configuration bits, allowing versatile mapping of complex gates or small arithmetic units. For instance, flip-flops paired with each LUT provide state retention, configurable as edge-triggered registers or latches with optional clock enables and resets, enabling the realization of finite state machines or pipelines. In the seminal Xilinx Virtex family introduced in 1998, each CLB contains four 4-input LUTs and four flip-flops organized into two slices, arranged in a rectangular array such as 64 rows by 96 columns for the XCV1000 device, supporting densities up to 1 million system gates. Resource utilization metrics, such as slices per logic function, guide design optimization; a typical slice might implement 4-8 equivalent gates or a single 4-bit adder, depending on the function's complexity.[36] Routing in FPGAs is facilitated by segmented wiring channels and switch matrices that connect CLBs and IOBs, with programmable switches—implemented via pass transistors or multiplexers—controlling signal paths for arbitrary connectivity. These interconnect resources, including short single-length wires, medium-length buffered lines, and long lines spanning the chip, occupy 80-90% of the total die area to accommodate the high fan-out typical of logic designs. IOBs, positioned along the chip periphery, interface with external signals, incorporating programmable buffers, pull-up resistors, and support for standards like LVTTL, ensuring seamless integration with surrounding systems.[36]Routing and Interconnect Resources

The routing and interconnect resources in field-programmable gate arrays (FPGAs) form a programmable network that connects configurable logic blocks (CLBs) and other elements, enabling flexible signal distribution across the device.[37] This network is essential for FPGA scalability and performance, as it determines how efficiently signals can propagate without excessive delay or resource overuse.[38] In the predominant island-style architecture, CLBs are arranged as discrete "islands" embedded within a "sea" of routing interconnects, where horizontal and vertical channels surround each CLB to facilitate connections.[36] This contrasts with sea-of-gates architectures, which distribute logic more uniformly without distinct block boundaries, though island-style remains the standard for modern commercial FPGAs due to its balance of flexibility and routability.[39] Interconnect resources are categorized by their scope and purpose, including local, global, and express types. Local interconnects consist of short wires that link adjacent CLBs or within a CLB cluster, typically spanning one or a few tiles for low-delay, intra-region signaling.[40] Global interconnects, often implemented as long lines spanning multiple CLBs across the chip, provide chip-wide connectivity for broad signal distribution, such as clocks or reset signals.[37] Express interconnects are dedicated high-speed paths that bypass standard routing for critical signals, reducing latency in high-performance applications by offering direct, low-resistance routes.[41] At the heart of the routing architecture are switch boxes, which manage connections between wiring segments at channel intersections. These are commonly designed using multiplexer-based structures, where programmable multiplexers select among incoming tracks to route signals, or buffered pass-gate configurations that employ transistor gates controlled by configuration memory for efficient switching with minimal area overhead.[41] Routing channels, running horizontally and vertically between CLBs, have a defined width measured in tracks per channel, typically ranging from 24 to 200 tracks depending on the FPGA family and density, to accommodate the required connectivity density.[42] Key challenges in FPGA routing include congestion, where high demand for limited tracks in dense regions leads to unroutable designs or increased delays, and accurate delay modeling to predict signal propagation. Congestion is mitigated through place-and-route algorithms that balance resource allocation, but it remains a primary limiter of circuit density.[38] Delay modeling often employs the Elmore delay approximation to account for RC parasitics in segmented wires and switches, providing a first-order estimate of signal settling time crucial for timing closure.[43] Commercial tools like AMD's Vivado handle place-and-route by optimizing these resources, using iterative negotiation to resolve congestion and meet timing constraints.[44]Modern Enhancements and Variants

Modern field-programmable gate arrays (FPGAs) have evolved significantly since the 2010s through the integration of hardened intellectual property (IP) blocks, enabling higher performance and reduced power consumption in system-on-chip (SoC) designs. These enhancements include specialized DSP slices, such as Xilinx's DSP48 and DSP58 engines, which provide efficient multiply-accumulate operations for signal processing tasks.[45] PCIe interfaces are commonly hardened, as seen in Intel's Stratix 10 and Agilex families, supporting high-speed data transfer up to Gen5 rates for host-accelerator connectivity.[46] Additionally, embedded ARM processors, like the quad-core Cortex-A53 in AMD's Zynq UltraScale+ MPSoCs, allow seamless fusion of programmable logic with scalar processing for adaptive computing platforms.[47] A key advancement in scalability is 3D stacking via technologies like AMD's Stacked Silicon Interconnect (SSI), first introduced in Virtex UltraScale+ devices and extended to the Versal architecture announced in 2018, which stacks multiple dies to achieve higher density and bandwidth while improving power efficiency by minimizing interconnect distances.[48] This heterogeneous integration reduces size, weight, and power (SWaP) compared to traditional planar designs, enabling applications requiring massive parallelism.[49] Variants of modern FPGAs emphasize adaptive SoC capabilities and edge computing. Intel's Agilex 5 series (2024), incorporates AI Tensor Blocks for accelerated deep learning inference, offering up to 1.9x fabric performance over prior generations and supporting heterogeneous integration via Embedded Multi-Die Interconnect Bridge (EMIB).[50] For low-power edge deployments, Lattice Semiconductor's Certus-NX family, built on 28 nm FD-SOI process since 2020, delivers up to 4x lower power than comparable FPGAs, with features like programmable back-bias for mode selection between low-power and high-performance operation, ideal for instant-on sensor interfaces.[51] By 2023, AMD's Versal Premium series on TSMC's 7 nm process achieved densities exceeding 10 million logic cells, with the VP1902 model offering 18.5 million system logic cells for emulation and acceleration tasks, doubling programmable logic density over predecessors.[52] Performance highlights include up to 99 TOPS (INT8) from enhanced DSP58 engines and support for 600G multirate Ethernet, enabling 5 Tb/s aggregate throughput for data-centric workloads.[52] Power efficiency gains stem from advanced nodes and optimized architectures, such as FD-SOI in edge variants, reducing soft error rates by 100x.[51] Looking to 2025 trends, FPGAs are incorporating quantum-resistant cryptography support, as exemplified by Lattice's MachXO5-NX TDQ family, the first CNSA 2.0-compliant post-quantum cryptography (PQC)-ready devices with hardware root of trust and crypto-agility for secure edge and data center applications.[53] Densities continue surpassing 10 million cells, with forthcoming shifts to sub-7 nm processes like TSMC's 5 nm enhancing efficiency for AI and high-bandwidth networking, including 100G+ Ethernet standards.[52]Configuration Mechanisms

Memory Technologies for Retention

Some programmable logic devices (PLDs), particularly erasable and reprogrammable types, rely on non-volatile memory technologies to retain configuration data without continuous power supply, ensuring persistent logic functionality across power cycles. These technologies form the basis for storing the device's programmable interconnections and logic states, with key types including antifuse, and floating-gate-based EEPROM and flash memory. Factory-based mask programming, used in some read-only memories (ROMs) and early PROMs, involves custom photomasks to define permanent metal or polysilicon interconnections during fabrication, providing high-volume, cost-effective solutions for fixed designs but lacking user reprogrammability after manufacturing.[54] Antifuse technology employs a dielectric layer between two metal layers that, when subjected to a high programming voltage, undergoes dielectric breakdown to form a permanent low-resistance conductive link, enabling one-time programmable (OTP) configurations in devices like Actel's ProASIC family. This physical alteration ensures indefinite data retention without power, as the connection persists structurally, offering superior reliability in radiation-hardened environments such as space applications, where long-term storage tests on amorphous silicon antifuses demonstrate stability over decades.[55][56] In contrast to reprogrammable options, antifuses provide exceptional endurance for static designs but cannot be erased or modified post-programming. Floating-gate EEPROM, a cornerstone of erasable PLDs like Generic Array Logic (GAL) devices from Lattice Semiconductor, stores configuration data as trapped charges on an isolated polysilicon gate within a MOSFET structure, altering the transistor's threshold voltage to represent logic states. Programming injects electrons onto the floating gate via Fowler-Nordheim tunneling under high voltage, while electrical erasure removes them, allowing in-system reprogramming; GAL devices, such as the GAL16V8, utilize these E²CMOS EEPROM cells for their AND-array configuration, typically comprising tens to hundreds of bits per device. Data retention in these non-volatile cells stems from the insulating oxide layers that minimize charge leakage, with typical lifespans of 10 to 20 years at room temperature, though accelerated testing at elevated temperatures confirms this through Arrhenius modeling of charge detrapping.[57] Charge trapping in the tunnel oxide during repeated program/erase cycles can cause threshold voltage shifts, but optimized designs mitigate this for reliable operation.[58] Flash memory, an evolution of EEPROM used in Complex Programmable Logic Devices (CPLDs) like Xilinx's XC9500 series, employs similar floating-gate mechanisms but enables block-level electrical erasure for faster reconfiguration, storing configuration bits in dense arrays— for instance, the XC9572XL CPLD features an integrated flash array supporting up to several thousand configuration bits. Retention characteristics mirror EEPROM, with non-volatile charge storage providing 20 years of data integrity under standard conditions, as verified in manufacturer specifications for industrial applications.[59] Trade-offs between these technologies highlight antifuse's unmatched permanence and radiation tolerance against EEPROM and flash's reprogrammability, where the latter offer 10,000 to 1,000,000 write/erase cycles before oxide degradation impacts retention, balancing flexibility with endurance limits in iterative design environments.[57][60] Emerging non-volatile memory technologies, such as magnetoresistive random-access memory (MRAM), are being explored for integration into FPGAs and PLDs as of 2025, offering instant-on reconfiguration, lower power, and resistance to radiation without the volatility of SRAM or limitations of flash.[61]Volatile and Non-Volatile Approaches

Volatile approaches to configuration in programmable logic devices (PLDs), primarily SRAM-based field-programmable gate arrays (FPGAs), rely on static random-access memory cells to store the device logic and interconnect settings. This method enables rapid reconfiguration, typically completing in hundreds of milliseconds to seconds for full device updates in modern implementations, with partial reconfiguration allowing faster selective updates often in milliseconds, making it suitable for applications requiring frequent or partial runtime changes without halting the entire system. However, SRAM's volatility means the configuration is lost upon power cycling, necessitating an external boot process—typically loading a bitstream from non-volatile storage like flash memory—each time the device powers up, which introduces a brief delay before functionality resumes. Partial reconfiguration, a key feature of SRAM-based FPGAs, allows selective updating of device regions while the rest continues operating uninterrupted, enhancing efficiency in dynamic environments such as adaptive signal processing or real-time systems.[62] Non-volatile approaches, commonly implemented in complex programmable logic devices (CPLDs) using embedded flash or EEPROM cells, retain configuration data indefinitely without power, enabling instant-on operation upon power-up with no external boot required. This eliminates reconfiguration delays and supports boot-critical applications where immediate availability is essential, such as power sequencing or system initialization in embedded controllers. Radiation-hardened variants of these non-volatile PLDs, like Microchip's RTG4 flash-based FPGAs (which share architectural similarities with CPLDs in configuration), withstand high-radiation environments in space or nuclear settings by leveraging flash's inherent resilience to single-event upsets, often achieving total ionizing dose tolerance exceeding 100 krad. These devices prioritize reliability in harsh conditions, with flash cells designed to maintain data integrity under ionizing radiation.[63] Hybrid configurations combine SRAM's speed with non-volatile storage, typically using flash or EEPROM as a shadow memory that automatically copies the bitstream to SRAM cells during power-up, achieving reconfiguration times in hundreds of milliseconds to seconds while providing retention. This approach balances volatility's flexibility with non-volatility's persistence, common in devices like Actel's Fusion family, where flash holds the persistent image and SRAM drives runtime logic. In terms of power impacts, volatile SRAM-based PLDs consume higher static power—often exceeding 100 mW in mid-range FPGAs due to constant refresh needs—making them preferable for dynamic applications like machine learning accelerators that tolerate elevated consumption for reconfigurability. Conversely, non-volatile flash-based PLDs exhibit lower standby power, around 50 mW or less, suiting boot-critical uses in battery-powered or low-power systems where minimizing idle draw is vital. Hybrids mitigate this by leveraging flash's low retention power during off-states but incur slight overhead from boot-time transfers.[64][65][66] Retention in non-volatile PLDs is rigorously tested per JEDEC standards like JESD22-A117, which evaluates EEPROM endurance and data retention over expected lifetimes, often projecting 10-20 years at elevated temperatures to ensure long-term reliability in deployed systems. Anti-tamper features further enhance security in both volatile and non-volatile PLDs; for instance, modern FPGAs and CPLDs incorporate bitstream encryption, physical sensors for voltage/clock anomalies, and automatic data erasure upon detected intrusion, as outlined in 2025 DoD guidance for FPGA security, preventing reverse engineering or unauthorized reconfiguration in sensitive applications like defense electronics. These mechanisms, including device-level monitors in Lattice Avant-X and Microchip PolarFire families, respond to tampering by clearing configuration memory, thereby protecting intellectual property.[67][68][69]Programming and Design Flow

Hardware Description Languages

Hardware description languages (HDLs) serve as the primary means for specifying the logic functionality of programmable logic devices (PLDs), enabling designers to model hardware behavior at various abstraction levels for synthesis into device-specific structures such as macrocells in complex PLDs (CPLDs) or lookup tables (LUTs) in field-programmable gate arrays (FPGAs). These languages facilitate the creation of reusable, verifiable designs that can be simulated prior to implementation, ensuring correctness before configuration.[8] Verilog, standardized as IEEE 1364, is an event-driven HDL that uses modules to encapsulate logic, with constructs like always blocks for describing sequential behavior and continuous assignments for combinational logic. For instance, a simple RTL description of a logic gate in Verilog might appear as:module logic_gate (

input a, b, c,

output out

);

assign out = (a & b) | (~c);

endmodule

module logic_gate (

input a, b, c,

output out

);

assign out = (a & b) | (~c);

endmodule

entity logic_gate is

port (

a, b, c : in bit;

out : out bit

);

end entity logic_gate;

architecture behavioral of logic_gate is

begin

out <= (a and b) or (not c);

end architecture behavioral;

entity logic_gate is

port (

a, b, c : in bit;

out : out bit

);

end entity logic_gate;

architecture behavioral of logic_gate is

begin

out <= (a and b) or (not c);

end architecture behavioral;